# A 0.5-Watt 47-GHz Power Amplifier Using GaAs Monolithic Circuits

G. Hegazi, K. Pande, F. Phelleps, E. Chang, A. Cornfeld, P. Rice, M. Ghahremani, and P. Pages

**Abstract**— 47-GHz Monolithic microwave integrated circuit (MMIC) power amplifier chips have been developed using 0.35-mm gate-length molecular beam epitaxial (MBE) MESFET technology. The amplifier chips have been assembled in a waveguide package to constitute a 47 GHz power amplifier with nominal output power of 0.4 Watt and 15 dB of gain. The saturated output power of this amplifier exceeded 0.5 Watt. These power and gain results might represent the highest reported to date at this frequency from an MMIC amplifier utilizing 0.35-mm gate-length MESFET. This amplifier has an application as a driver for a monolithic doubler circuit to reliably produce greater than 80 mW of output power at 94 GHz for missile seeker application.

## I. INTRODUCTION

**94**-GHz monolithic power transmitters have potential applications for W-band missile seekers and phased array radars. However, no such transmitters are readily available due to the lack of power amplifiers with desired output power (e.g., 80 mW) at 94 GHz. Although pseudomorphic InGaAs and lattice matched InP high-electron mobility transistors with multi-quantum well structures show excellent potential for power amplification at W-band [1]–[3], their usage is limited due to relatively low yield as a result of 0.1 m gate lengths. Moreover, their reliability has yet to be established for power applications. Therefore, the option of doubling 47 GHz of power to 94 GHz is quite attractive since reliable, high yield 0.35-mm gate-length FET's can be used for the 47 GHz power amplifier chips [4], [5].

## II. AMPLIFIER CONFIGURATION

The amplifier comprises two types of chips: driver chips (type A) and power chips (type B). A microphotograph of both types of chips is shown in Fig. 1. The driver chip utilizes a 0.4-mm FET while the power chip utilizes two 0.4 mm FET devices combined in parallel. The baseline monolithic driver chip design consists of single-stage, 0.4-mm FET power amplifier with dc blocking capacitors and on-chip bias and stabilization networks. The power chip consisted of two driver chips combined in parallel using integrated Wilkinson type divider/combiner circuits. A small signal equivalent circuit was obtained for the MESFET device by matching its measured *S*-parameters to its equivalent circuit *S*-parameters. The optimum load impedance, required by the MESFET to deliver its

Fig. 1. Microphotograph of 47-GHz amplifier chips (A and B types).

maximum output power at 47 GHz, was calculated with a load pull program that uses the device equivalent circuit and its dc parameters in the simulation process as described in [6]. In the MMIC circuit design, the output matching circuit presented the optimum output impedance to the MESFET in its bandwidth of operation, thus, achieving maximum power in that bandwidth. The input matching circuit was designed by conjugate matching the MESFET input impedance with that device, terminated with the optimum load impedance to achieve maximum gain. The source and load match were then optimized for input return loss and gain flatness across the bandwidth of operation by using Touchstone microwave circuit analysis program. A stabilizing RC circuit was integrated with the gate bias network to ensure unconditional stability of the chip operation down to few MHz frequency range. A potential divider circuit was also included at the input to the gate of the FET to scale the available power supply voltage of -5 V of the system to a nominal value of -0.8 V. At the drain side, the +5 V power supply voltage of the system was applied without scaling to the bias circuit of the drain.

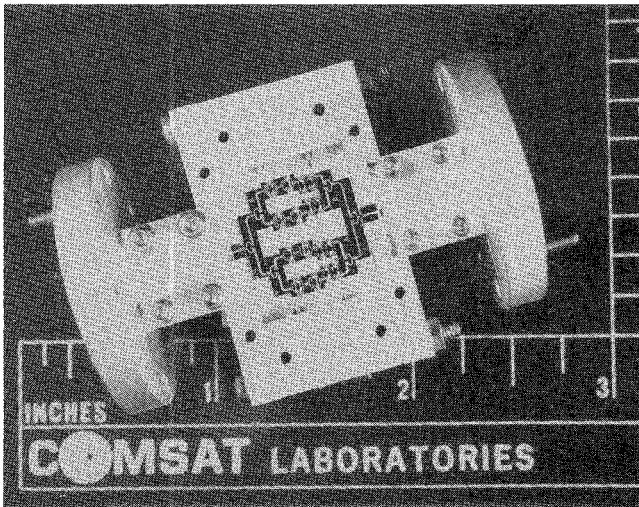

The previous two types of chips were used to construct the four-way combined amplifier as is shown in Fig. 2. The hybrid dividers and combiners used were regular and offset Wilkinson type circuits fabricated on 5-mil fused silica substrates. The chips, together with the combiners, were mounted on a flat center block that was then sandwiched between two ridged waveguide-to-microstrip transitions.

## III. AMPLIFIER PERFORMANCE

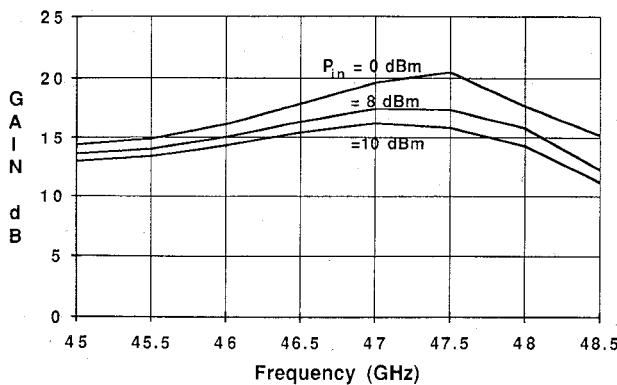

The amplifier was RF tested using a U-band waveguide setup. The gain is shown vs frequency in Fig. 3 for three input drive levels, namely 0, 8, and 10 dBm. The amplifier gain is

Manuscript received September 25, 1991

G. Hegazi, K. Pande, and F. Phelleps, E. Chang, and A. Cornfeld are with COMSAT Laboratories, 22300 Comsat Dr., Clarksburg, MD 20871.

P. Rice, M. Ghahremani, and P. Pages are with Hercules Defense Electronics Systems, P.O. Box 4648, Clearwater, FL 34618.

IEEE Log Number 9105537.

Fig. 2. Assembled 47-GHz 0.5-Watt power amplifier.

Fig. 3. Measured gain vs. frequency of the amplifier for three input drive levels.

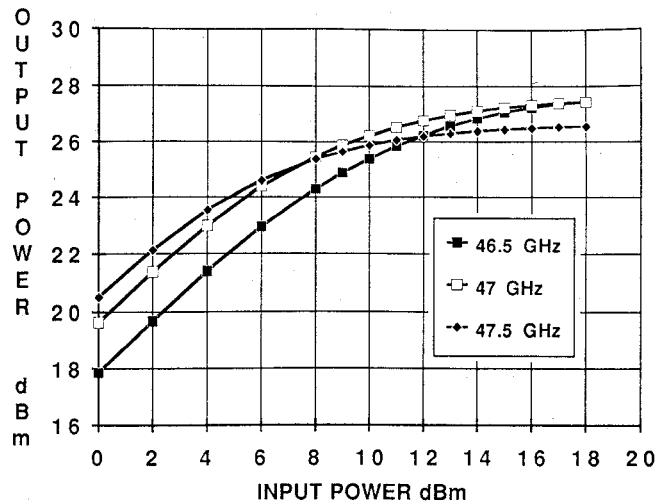

about 15 dB across the bandwidth from 46.5 to 47.5 GHz with an output power level of 0.4 W. The input power vs. output power of the amplifier is shown in Fig. 4 for three frequencies, namely, 46.5, 47, and 47.5 GHz. It is seen that the saturated 47-GHz output power of the amplifier exceeded 0.5 W. The dc power consumption of this amplifier is 5 V and 1.85 A.

The reliability of the amplifier operation was checked by performing a thermal measurement using infrared analysis. The measured junction temperature of the FET devices was 40°C maximum at room temperature. Since this FET can operate reliably with a junction temperature below 135°C, these results indicate that the amplifier can operate reliably up to an ambient temperature of 90°C.

#### IV. CONCLUSION

A 47-GHz power amplifier was demonstrated using high-

Fig. 4. Measured input power vs. output power of the amplifier at 46.5, 47, and 47.5 GHz.

yield, reliable MMIC power amplifier chips. The amplifier delivers a saturated output power exceeding 0.5 W at 47 GHz, and has a nominal output power of 0.4 W with a gain of 15 dB from 46.5–47.5 GHz. This amplifier has potential application as a driver for a monolithic frequency doubler to obtain power at 94 GHz.

#### ACKNOWLEDGMENT

The authors thank Dr. R. Schwarz and Dr. H. Huang for supporting this program, and J. Singer and J. Proctor for the assembly and testing of the amplifier.

#### REFERENCES

- [1] G. Metze, T. Lee, J. Bass, P. Laux, H. Carlson, and A. Cornfeld, "A narrow-channel 0.2 m gate-length, double-quantum-well pseudomorphic MODFET with high power gain at millimeter-wave frequencies," *IEEE Electron Device Lett.*, vol. 11, pp. 493–495, Nov. 1990.

- [2] R. Majid-Ahy, M. Riazat, C. Nishimoto, M. Glenn, S. Silverman, S. Weng, Y. Poa, G. Zdziak, S. Bandy, and Z. Tan, "5–100 GHz InP CPW MMIC 7-section distributed amplifier," *IEEE Microwave Millimeter-Wave Monolithic Circuits Symp. Tech. Dig.*, May 1990, pp. 31–34.

- [3] P. M. Smith, M.Y. Koa, P. Ho, P. C. Chao, K. H. G. Duh, A. A. Jabra, R. P. Smith, and J. M. Ballingall, "A 0.15 m gate-length pseudomorphic HEMT," *IEEE-MTT-S Symp. Dig.*, 1989, pp. 983–986.

- [4] G. Hegazi, A. Ezzeddine, F. Phelleps, P. McNally, K. Pande, P. Rice, and P. Pages, "W-band monolithic frequency doubler using a vertical GaAs varactor diode with  $n+$  buried layer," *Electron. Lett.*, vol. 27, no. 3, pp. 213–214, Jan. 1991.

- [5] G. Hegazi, E. Chang, J. Singer, F. Phelleps, P. McNally, K. Pande, P. Rice, and P. Pages, "A W-band doubler/amplifier chain using a MMIC varactor doubler and a MMIC power MESFET amplifier," *IEEE-MTT-S Symp. Tech. Dig.*, June 1991, pp. 933–936.

- [6] G. Hegazi, H. Hung, F. Phelleps, L. Holdeman, A. Cornfeld, T. Smith, J. Allison, and H. Huang, "V-band monolithic power MESFET amplifiers," *IEEE-MTT-S Symp. Dig.*, June 1989, pp. 409–412.